为尽量降低高频范围内的环路阻抗,需要降低电容器的ESL和线路的电感。如果能够进行巧妙地设计,可以将双层基板的总电感降低至约几nH,多层基板则可降低至1nH或以下。在图3-4-9的示例中,其值约为0.3nH。

(1) 使用低ESL电容器

每个电容器(如果是MLCC)的ESL约为0.5nH,在总电感中占很大一部分。为降低此值,可使用低ESL电容器,具体将在第6章中讲述。低ESL电容器也在村田官网中进行了详细介绍。

(2) 降低线路电感

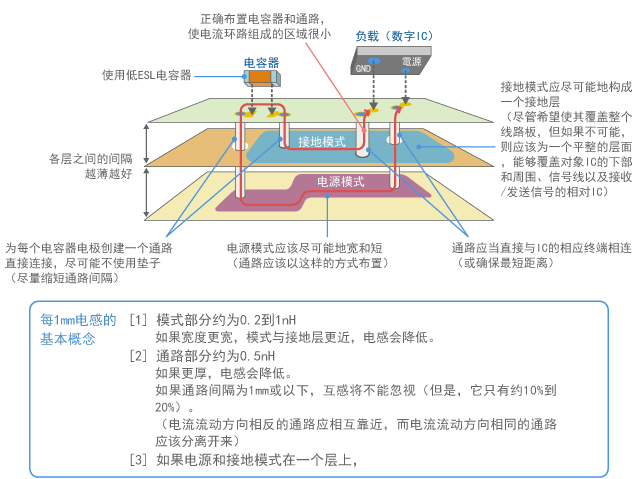

要降低线路和通孔中的电感,线路和通孔应该要“粗且短”。例如,在布置电容器和通孔时,应减少图3-4-10中所示电流环路的面积。此外,布局模式应该尽可能地宽。将电容器放置在(基板另一侧)IC的正下方,并使基板变薄,通常能够让电流环路变小。

(3) 电容器和通孔的并联

当并联使用众通孔通路和电容器时,可降低阻抗。

因为线路和通孔的电感非常小,而且还涉及互感,所以很难得到一个简单的判断。为此,可使用电磁模拟装置估计这样的环路阻抗。图3-4-12给出了电感的一般范围供您参考。但是,根据线路的不同形状,电感可能相差好几倍。此外,即使只是1mm的长度,也会造成约0.5nH的电感,这是无法忽略的。

图3-4-12 降低环路阻抗的电容器布置

(4) 注意反谐振

如果使用了两个或更多个电容器,需要考虑电容器之间发生的谐振。一般而言,如果并联连接具有不同自谐振频率的多个电容器,反谐振会导致具有高阻抗的频率(将在第6章中进行探讨)。

除了线路电感之外,还需要考虑在100MHz以上的高频范围内存在的静电容量。此外,电源层的谐振和IC封装的影响也会在高频范围内变得显著。鉴于要素如此复杂,也可使用电磁模拟装置。