(1) 源阻抗的频率范围

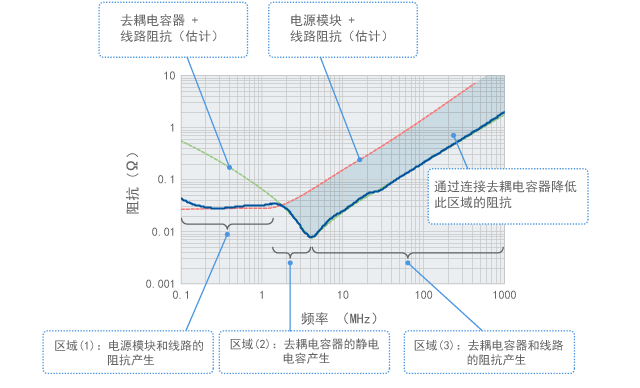

图3-4-5中所示的源阻抗实际上给出了一个例子,其通过使用多个去耦电容器实现了极低的阻抗。这些频率特征可以分为如图3-4-9所示的三个区域。

(2) 什么控制着低频范围?

①的低于1MHz较为平缓部分可观察到的电源模块输出阻抗。如果不使用去耦电容器,阻抗会从图中虚线所指示的较低频率处开始增加。这是因为电源模块的输出特征和线路中电感的作用。

如果使用去耦电容器,可抑制高频范围的阻抗。

(3) 什么控制着高频范围?

图3-4-9中(2)和(3)指示的是相对较高的频率范围,在其中可观察到去耦电容器的阻抗。(2)是电容器存在电容阻抗的频率范围,可通过将静电容量的大小进行一定程度地控制。(3)是电容器存在电感阻抗的频率范围。为进一步降低此区域的阻抗,需要降低去耦电容器的ESL,或者降低连接至电容器线路的电感。

图3-4-9 源阻抗的频率特征及发挥作用的元件

(4) 环路阻抗

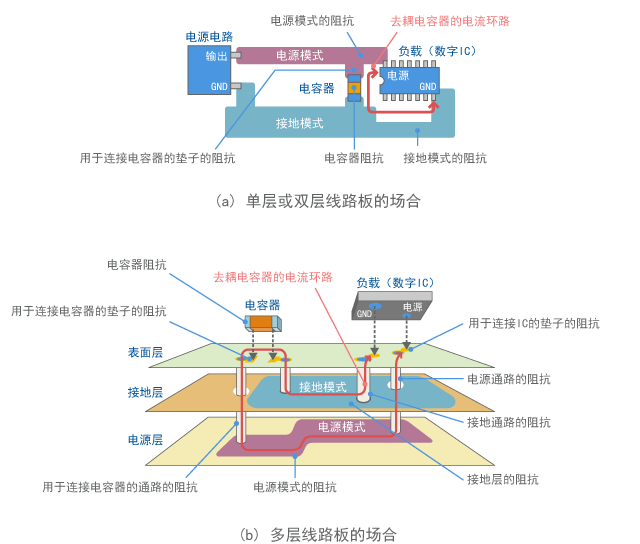

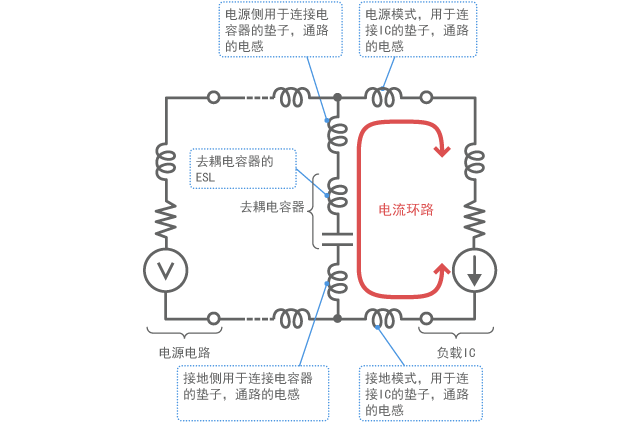

线路电感由负载IC和去耦电容器之间连接的模式和通孔构成,如图3-4-10中所示。将经过这些元件的整个电流环路之和与电容器的ESL相加,可得出总电感。图3-4-11为等效电路。

去耦电容器所建立电流环路的阻抗可以称为环路阻抗。图3-4-9所示区域(3)的环路阻抗是主要来自线路和电容器本身的电感所致。

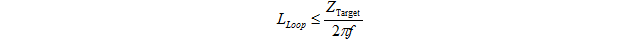

为降低高频范围内的环路阻抗,需要降低电感。也就是说,当环路阻抗的目标值为ZTarget (Ω),频率为ƒ(Hz),总阻抗为LLoop (H),可得出如下公式:

(公式3-4-1)

例如,如果需要将100MHz处的环路阻抗降低到1Ω或更少,总阻抗需要约为1.6nH或以下。这是一个极低的值。

(5) 环路阻抗的要素

因为实际电路可能存在导线分支的情况或者有多个电容器,所以不能像图3-4-10和图3-4-11那样简单地思考问题。但是,这个模型是有用的,可以作为将环路阻抗分解为各个要素的理念。为有效地尽量降低环路阻抗,需要降低在总阻抗中占很大一部分的电感。

图3-4-10 环路阻抗的要素

图3-4-11 去耦电路的等效电路