(1) 数字信号特性阻抗

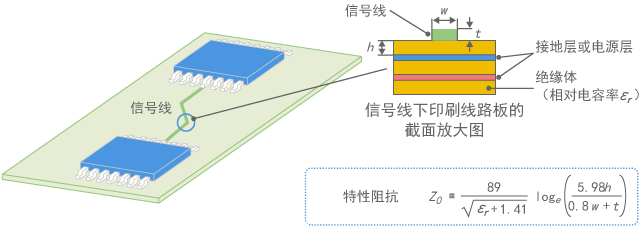

数字信号所使用信号线的特征阻抗有多大?如图3-3-6所示,在以电源层和接地层为内层的4层电路板的表面有一根信号线,此信号线可以作为微带线(以下称为MSL)来处理,其中信号线的特性阻抗约为50Ω到150Ω。(如果有电源线,特性阻抗值可能更小。)

(2) 很多数字电路都未实现阻抗匹配

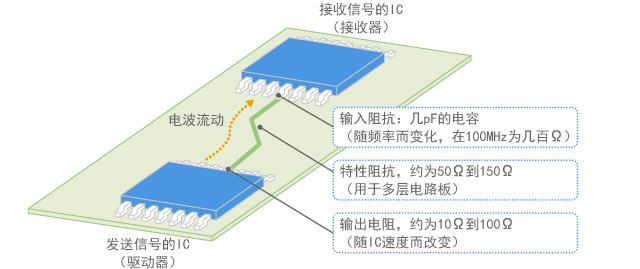

与此相反,数字IC的输入阻抗通常一个几pF的电容,在频率为100MHz及以下时,会变成100Ω以上的高阻抗。因此,如图3-3-7所示,数字电路的设计基本上会产生非常高的反射,从而导致在接收器处反射大部分信号能。

此外,数字IC驱动器侧的输出阻抗也会变化。因此,阻抗匹配并非总是在驱动器侧完成,而且也可能导致反射。所以,数字信号一般会在信号线两端造成反射(如图3-3-2所示),而且会在造成多重反射一定程度时被传输。

图3-3-6 信号线的特性阻抗

图3-3-7 数字信号线的阻抗匹配状态

(3) 驻波指示匹配状态

尽管为了便于解释在图3-3-4中分别描述了输入波和反射波,但在正常测量中很难单独观察这两种波形(因为示波镜只会显示复合波形)。因此,可以按照后面的讲述,通过观察驻波来确定反射状态。

如果因驱动器侧和接收器侧的反射而产生多重反射,传输线会形成一种谐振器,使某个特定的频率变得特别明显。从正确传输数字信号波形(即“信号完整性”)的角度而言,传输线产生的谐振并不可取,因为它会导致振铃。此外,从EMC的角度来看,这也是不可取的,因为它会在谐振频率处增加噪声。为抑制传输线产生的谐振,导线的两端或者一端应该靠近匹配状态,以便吸收反射。